| Лабораторные и практические работы по микропроцессорам |

|

Страница 5 из 8

Задания Задание 1 Построить временные диаграммы процесса формирования системных сигналов “ INT”, ”RESET”, “STEP”. Задание 2 Обратиться к ячейке ЗУ с адресом 0000 h. В этой ячейке расположен код операции первой команды системного монитора. Обращаясь последовательно к ячейкам ЗУ, записать текст программы начальной установки УМК до адреса 0052h в машинных кодах. Выполнить дизассемблирование кодов и проанализировать полученную программу начального запуска МП. При записи программы необходимо учитывать, что не запрограммированные ячейки РПЗУ содержат код FFh. Задание 3 По принципиальной электрической схеме (Рис. 17) определить адрес порта шагового режима УМК и данные для сброса и восстановления шагового режима работы МП. Написать и запустить на УМК в шаговом режиме программу для управления шаговым режимом работы МП с учетом задержки включения шагового режима на n машинных циклов. Определить число n по схеме включения счетчика задержки и проверить полученное значение приработе программы. Программу расположить с адреса 0800 h – верхней границы ОЗУ. Проследить процесс выполнения программы по двоичным индикаторам шин и состояния МП. Задание 4 С помощью процедуры "П" обратиться к адресу 035Bh. Это начальный адрес подпрограммы “DELAY” системного монитора. Назначение данной подпрограммы – формирование интервала времени (10 ms). Выполнить дизассемблирование подпрограммы “ DELAY”, составить алгоритм подпрограммы и проанализировать принцип формирования интервала времени программным путем. Составить и запустить программу формирования произвольного интервала времени, кратного 10 ms, c использованием подпрограммы “ DELAY” и регистров DE в качестве счетчика циклов обращения к подпрограмме. Задание 5 Составить и запустить программу для определения нижней границы оперативной памяти УМК. Объяснить разницу между адресом, полученным в результате работы программы, и адресом в счетчике SP при начальной установке УМК (граница доступной памяти). Задание 6 Составить и запустить программу для определения физических адресов произвольных фрагментов системных программ УМК. Текст системного монитора на ассемблере ВМ80 приведен в техническом описании УМК. Забиваем Сайты В ТОП КУВАЛДОЙ - Уникальные возможности от SeoHammer

Каждая ссылка анализируется по трем пакетам оценки: SEO, Трафик и SMM.

SeoHammer делает продвижение сайта прозрачным и простым занятием.

Ссылки, вечные ссылки, статьи, упоминания, пресс-релизы - используйте по максимуму потенциал SeoHammer для продвижения вашего сайта.

Что умеет делать SeoHammer

— Продвижение в один клик, интеллектуальный подбор запросов, покупка самых лучших ссылок с высокой степенью качества у лучших бирж ссылок. — Регулярная проверка качества ссылок по более чем 100 показателям и ежедневный пересчет показателей качества проекта. — Все известные форматы ссылок: арендные ссылки, вечные ссылки, публикации (упоминания, мнения, отзывы, статьи, пресс-релизы). — SeoHammer покажет, где рост или падение, а также запросы, на которые нужно обратить внимание. SeoHammer еще предоставляет технологию Буст, она ускоряет продвижение в десятки раз, а первые результаты появляются уже в течение первых 7 дней. Зарегистрироваться и Начать продвижение В качестве ассоциативного признака для поиска данного фрагмента рекомендуется использовать группу кодов за n строк программы. Интерфейс светодиодного индикатора Описание схемы Каждый разряд индикатора представлен одной микросхемой (Рис. 18) типа АЛС324. Знак воспроизводится семью светодиодными сегментами и восьмой сегмент воспроизводит запятую.

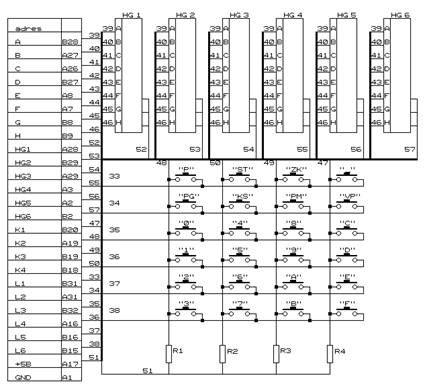

Рис. 18 Схема блока индикатора и клавиатуры Для включения любого из восьми сегментов необходимо подать высокий логический уровень (положительное напряжение) на общие аноды светодиодов данной микросхемы индикатора (выводы 3,9,14 микросхем индикатора) и низкий логический уровень (нулевое напряжение) на катоды светодиодов выбранных сегментов (выводы 1,13,10,8,7,2,11,6). Для управления микросхемами индикаторов необходимо два порта вывода: один для выбора разряда, другой для выбора сегмента в разряде индикатора. Оба порта организованы на базе БИС параллельного интерфейса КР580ВВ55 (Рис. 19).

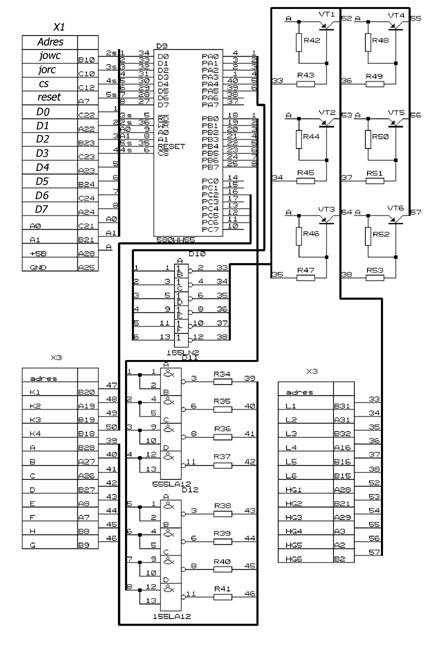

Рис. 19 Схема интерфейса индикатора и клавиатуры Общие аноды светодиодов сегментов каждой микросхемы индикатора по линиям 52-57 через разъем Х3 подключены к коллекторам транзисторов VT1-VT6. Транзисторы служат для согласования по мощности выходов микросхем и цепей анодов светодиодных сегментов. При анализе работы схемы необходимо учитывать, что транзисторы включены по схеме с общим эмиттером и выполняют операцию инверсии. Базовые цепи транзисторов подключены к каналу "А" БИС параллельного интерфейса ВВ55 (элемент D9) через инверторы D10. Канал "А" БИС интерфейса образует порт для выбора разряда индикатора. Выводы сегментов каждой микросхемы индикатора по линиям 39-46 через разъем Х3 и инверторы D11, D12 подключены к каналу "В" БИС интерфейса. Канал "В" образует порт управления светодиодными сегментами. Для обращения к указанным портам необходимо выполнение следующих условий:

Все перечисленные функции, кроме формирования сигналов WR и RD выполняются программным путем. Сигналы WR и RD формируются аппаратным путем при переходе МП в режим вывода или ввода (см. схему блока центрального процессора на Рис. 20). Рассмотренные аппаратные средства интерфейса индикатора образуют аппаратную среду, параметры которой должны быть определены при создании программных средств. Указанные параметры могут быть приведены в техническом описании устройства в виде перечней адресов и переменных или получены из анализа его работы по функциональным и электрическим принципиальным схемам. Кроме того, ряд параметров определяется из справочных данных на используемые микросхемы. Это относится к специализированным БИС, функции которых задаются табличным методом. Сервис онлайн-записи на собственном Telegram-боте

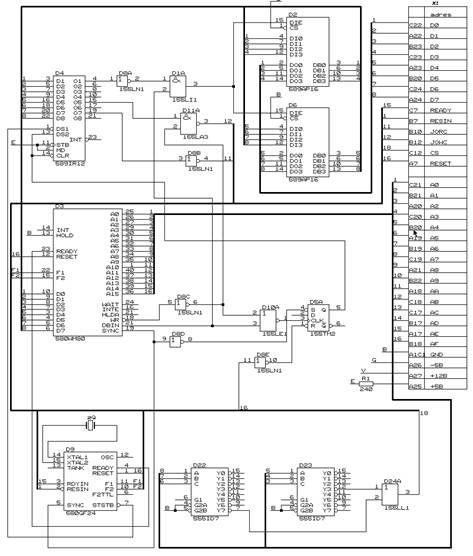

Попробуйте сервис онлайн-записи VisitTime на основе вашего собственного Telegram-бота:— Разгрузит мастера, специалиста или компанию; — Позволит гибко управлять расписанием и загрузкой; — Разошлет оповещения о новых услугах или акциях; — Позволит принять оплату на карту/кошелек/счет; — Позволит записываться на групповые и персональные посещения; — Поможет получить от клиента отзывы о визите к вам; — Включает в себя сервис чаевых. Для новых пользователей первый месяц бесплатно. Зарегистрироваться в сервисе В режиме вывода информации через порты, образованные каналами БИС интерфейса ВВ55 и при записи управляющего слова в регистр хранения управляющего слова необходимо обеспечить следующее состояние входов “ WR” и “RD”: “WR”=0 ; “RD”=1 Входы “RD” и “ WR” БИС интерфейса ВВ55 (см. Рис. 19) по линиям 3 и 2 через разъем Х1 соединены с линиями 11 и 12 блока центрального процессора (см. Рис. 20). На линии 11 системный сигнал “IORC” формируется инвертором D8, вход которого подключен к разряду Q6 регистра состояния. Низкий уровень системного сигнала “IORC” соответствует режиму ввода информации из внешнего устройства. На линии 12 системный сигнал “ IOWC” формируется элементом D11 (штрих Шеффера). Низкий уровень системного сигнала “ IOWC” соответствует режиму вывода информации во внешнее устройство.

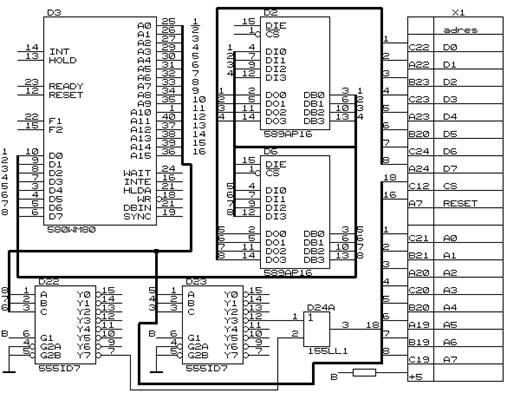

Рис. 20 Схема базового блока центрального процессора Вход “CS” выбора микросхемы D9 (см. Рис. 20) соединен через разъем Х1 с линией 18 в блоке центрального процессора. Системный сигнал “CS” на линии 18 формируется элементом D24 (дизъюнкция), входы которого соединены с инверсными выходами двух дешифраторов D22, D23 (155ИД4). Это полные трехразрядные дешифраторы с дополнительными входами стробирования и инверсным унитарным кодом на выходе. Дешифраторы D22, D23 используются для формирования адресов четырех портов: три канала ввода-вывода и регистр управляющего слова БИС интерфейса ВВ55. Входы дешифраторов соединены с разрядами младшего байта системной шины адреса, сформированной шинными формирователями D15 - D18 (К589АП16). На Рис. 21 показаны основные элементы схемы блока центрального процессора, участвующие в формировании адресов параллельного интерфейса.

Рис. 21 Основные элементы схемы блока центрального процессора Входы А0, А1 БИС параллельного интерфейса (см. Рис. 19) непосредственно подключены к разрядам А0, А1 системной шины адреса (см. Рис. 20 и Рис. 21) Эти разряды используются для обращения к каналам и регистру управляющего слова БИС интерфейса. Задание 7 Составить электрическую принципиальную схему подключения одного разряда светодиодного индикатора к БИС интерфейса и схему формирования управляющих сигналов БИС интерфейса. Задание 8 На основе анализа работы схемы (задание 7) разработать и запустить на УМК программу для выхода на произвольные сегменты одного из разрядов светодиодного индикатора. Задание 9 Составить и запустить на УМК программу для вывода на один из разрядов индикатора последовательности знаков шестнадцатеричной системы счисления. Время свечения каждого знака 1с. Для формирования заданного интервала времени рекомендуется использовать подпрограмму “DELAY” системного монитора. Для получения кодов знаков необходимо обратиться к алфавиту системного монитора, физический адрес которого определить по ассоциативному признаку (см. задание 6).

|