| Лабораторные и практические работы по микропроцессорам |

|

Страница 7 из 8

Задание 19 Составить и запустить программу для измерения периода следования импульсов, поступающих на один из разрядов канала "А" БИС интерфейса. Определить:

В качестве источника импульсной последовательности используется лабораторный импульсный генератор при уровне выходного импульсного сигнала 4,5 В положительной полярности. Подключение нестандартного оборудования к параллельному порту компьютера Описание схемы Основное назначение параллельного порта компьютера – подключение принтера ( LPT – Line PrinTer) и другого периферийного оборудования (сканер, HD и CD накопители и др.). LPT порт используется также, наряду с COM портом, для подключения к компьютеру нестандартного оборудования, например, микропроцессорных контроллеров, что позволяет при создании микропроцессорных систем многоуровневого типа использовать принцип распределения функций между вычислительными средствами нескольких уровней и оптимально решать задачи управления. В исходном варианте параллельный порт компьютера представляет собой совокупность из следующих компонентов:

Максимальная скорость передачи информации через стандартный параллельный порт не превышает 150 Кбайт/с. В настоящее время существуют более совершенные модификации LPT портов для скорости передачи до 2000 Кбайт/с:

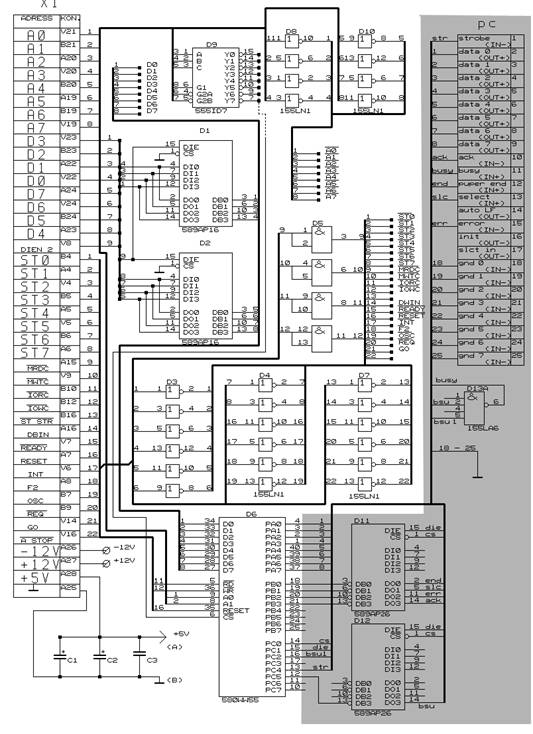

Спецификации режимов, физические параметры и требования к программному обеспечению представлены в стандарте IEEE 1284, который был окончательно принят в 1994 г. В лабораторной работе используется базовая модификация LPT порта с разъемом типа DB25. Параллельный порт компьютера, на основе которого организован LPT порт, состоит из трех регистров, расположенных относительно одного из двух базовых адресов пространства ввода-вывода компьютера. В компьютерах первых поколений регистры параллельного порта были расположены в контроллере параллельного обмена, аналогичном микросхеме 580ВВ55. В современных компьютерах регистры порта расположены в процессоре обмена высокой степени интеграции, который обеспечивает работу всех портов. На Рис. 24 представлена схема интерфейса для передачи информации в учебный микропроцессорный комплекс из компьютера через порт LPT. На макетном поле платы расширения М1 расположены дополнительные элементы, выделенные на Рис. 24: Забиваем Сайты В ТОП КУВАЛДОЙ - Уникальные возможности от SeoHammer

Каждая ссылка анализируется по трем пакетам оценки: SEO, Трафик и SMM.

SeoHammer делает продвижение сайта прозрачным и простым занятием.

Ссылки, вечные ссылки, статьи, упоминания, пресс-релизы - используйте по максимуму потенциал SeoHammer для продвижения вашего сайта.

Что умеет делать SeoHammer

— Продвижение в один клик, интеллектуальный подбор запросов, покупка самых лучших ссылок с высокой степенью качества у лучших бирж ссылок. — Регулярная проверка качества ссылок по более чем 100 показателям и ежедневный пересчет показателей качества проекта. — Все известные форматы ссылок: арендные ссылки, вечные ссылки, публикации (упоминания, мнения, отзывы, статьи, пресс-релизы). — SeoHammer покажет, где рост или падение, а также запросы, на которые нужно обратить внимание. SeoHammer еще предоставляет технологию Буст, она ускоряет продвижение в десятки раз, а первые результаты появляются уже в течение первых 7 дней. Зарегистрироваться и Начать продвижение

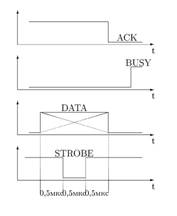

Драйвер, управляющий интерфейсом со стороны УМК, должен эмулировать функции интерфейса принтера, что дает возможность использовать стандартные системные функции компьютера (например COPY PRN) без обращения непосредственно к регистрам параллельного порта. В качестве режима работы БИС интерфейса может быть выбран режим “1”. В режиме “1” часть сигналов формируется аппаратно, что существенно упрощает драйвер и позволяет принимать короткие сигналы, которые не обработать программными методами, например, сигнал стробирования посылки данных, длительность которого 0,5 мкс.

Рис. 24 Схема параллельного порта для связи с компьютером через LPT Эмуляция интерфейсных функций принтера позволяет использовать для передачи стандартные системные средства компьютера. На Рис. 25 представлены временные диаграммы сигналов LPT порта.

Рис. 25 Временные диаграммы работы порта LPT Через параллельный порт (при наличии драйвера со стороны УМК) могут быть переданы и записаны в ОЗУ УМК любые данные из компьютера, представленные в виде отдельного файла. Для создания двухуровневой системы, содержащей микропроцессорные контроллеры на нижнем уровне и компьютер на верхнем уровне, необходимо представить данные в формате микропроцессора, а для загрузки программы необходимо сформировать файл из машинных кодов микропроцессора. Задание 20 Составить программу на языке ассемблера ВМ80 для формирования управляющих сигналов (сигналов статуса) на соответствующих линиях LPT порта. Запустить программу и проверить ее действие с помощью стандартных системных процедур. Задание 21 Составить программу драйвера для приема информации в УМК через параллельный порт компьютера. Драйвер должен выполнять следующие основные функции:

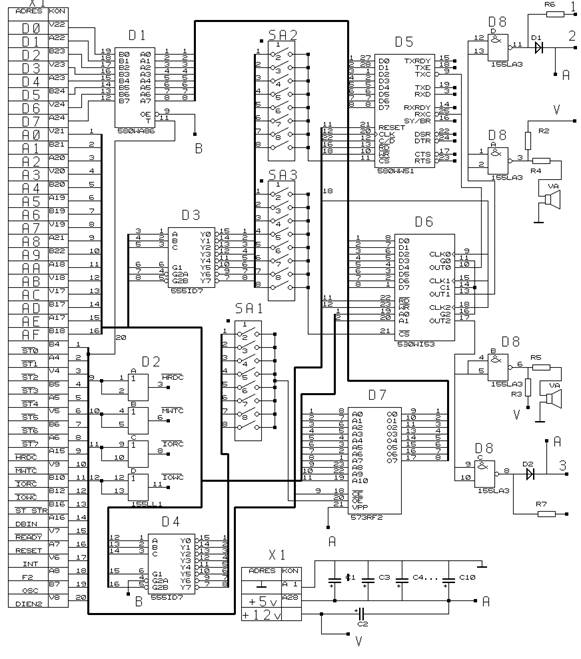

Выполнить загрузку в УМК произвольной программы через LPT порт. Таймер (плата ППИ) Описание схемы Блок таймера (плата расширения ППИ) устанавливается в системный разъем УМК и позволяет изучать работу БИС трехканального таймера КР580ВИ53 и последовательного приемопередатчика (последовательного интерфейса) КР580ВВ51.

Рис. 26 Схема блока таймера и последовательного порта ввода-вывода БИС таймера является многорежимным устройством с тремя независимыми каналами (портами), каждый из которых может быть запрограммирован отдельно. В персональных компьютерах первых поколений на основе отдельных микросхем таймера были построены системные часы, устройство регенерации информации в динамическом ОЗУ, акустический выход на встроенный громкоговоритель. В современных компьютерах аналогичные функции выполняются в интерфейсных микросхемах большой степени интеграции. Сервис онлайн-записи на собственном Telegram-боте

Попробуйте сервис онлайн-записи VisitTime на основе вашего собственного Telegram-бота:— Разгрузит мастера, специалиста или компанию; — Позволит гибко управлять расписанием и загрузкой; — Разошлет оповещения о новых услугах или акциях; — Позволит принять оплату на карту/кошелек/счет; — Позволит записываться на групповые и персональные посещения; — Поможет получить от клиента отзывы о визите к вам; — Включает в себя сервис чаевых. Для новых пользователей первый месяц бесплатно. Зарегистрироваться в сервисе В микропроцессорных контроллерах таймер выполняет функции счетчика внешних событий, генератора программируемых частот и другие функции реального времени. При работе с таймером КР580ВИ53 необходимо учитывать отсутствие входа для аппаратного сброса. Сброс каждого канала (начальная установка) происходит программным путем при обращении к регистру режима. На Рис. 26 представлена схема блока таймера. Дешифраторы К555ИД7 (D3, D4) используются для формирования адресов портов таймера ( D6) и последовательного интерфейса ( D5), а также дополнительного ПЗУ К573РФ2 (D7) емкостью 2 килобайта. Адреса портов таймера, последовательного интерфейса и ПЗУ определяется положением микропереключателей SA1, SA2, SA3. Входы синхронизации всех трех каналов таймера подключены по линии 18 к системной частоте синхронизации (Ф2). Выходы каналов 1 и 2 через инверторы D8 подключены к двухканальному акустическому излучателю ВА1, что дает возможность контролировать на слух результат работы таймера режиме формирования меандра в звуковом диапазоне частот. Выходы каналов 1 и 2 через инверторы D8 соединены с гнездами 1-4 для подключения внешних устройств и измерительных приборов. Канал 0 таймера используется для установки скорости обмена информацией в БИС последовательного интерфейса ВВ51. Для организации двунаправленной шины данных используется шинный формирователь К580ВА86 (D1). Двунаправленный шинный формирователь ВА86 обладает повышенной нагрузочной способностью, что позволяет подключать к шине данных большое число элементов, в т.ч. расположенных на макетном поле платы таймера при создании дополнительных аппаратных средств. Задание 22 Для заданного преподавателем положения переключателей SA1-3 определить адреса портов таймера. Задание 23 Составить и запустить программу для формирования заданной частоты (в пределах звукового диапазона) на выходе 1 и 2 таймера, работающего в режиме формирования меандра. Параметры сигнала на выходе таймера определить осциллографическим методом. Задание 24 Составить и запустить на УМК программу для изменения частоты по заданному закону на выходе 1 и 2 таймера, работающего в режиме формирования меандра. Задание 25 Составить и запустить программу для получения частотно модулированного импульсного сигнала. Параметры модуляции задаются преподавателем. Последовательный интерфейс (плата ППИ) Микросхема К580ВВ51 ( D5) (см. Рис. 26) предназначена для аппаратной реализации последовательного протокола обмена между центральным микропроцессором ВМ80 и каналами последовательной передачи дискретной информации. БИС ВВ51 может быть запрограммирована на выполнение любого из существующих протоколов обмена в синхронном и асинхронном режиме. Скорость обмена информацией устанавливается таймером ВИ53 (D6) по нулевому каналу.

|